# ACORN FLOPPY DSC CONTROLLER BOARD

# UNIT DESCRIPTION

### CONTENTS

| Para | graph      |                                                   | Page    |  |  |

|------|------------|---------------------------------------------------|---------|--|--|

| 1.   | INTRO      | ODUCTION                                          | 1       |  |  |

|      | 1.1        | General                                           | 1       |  |  |

|      | 1.2        | 1.2 Principles of Operation                       |         |  |  |

|      | 1.3        | Leading Particulars                               | 3       |  |  |

|      |            | 1.3.1 Mechanical                                  | 3       |  |  |

|      |            | 1.3.2 Power Supplies                              | 3       |  |  |

|      |            | 1.3.3 Connections                                 | 3       |  |  |

| 2.   | CIRCL      | JIT DESCRIPTION                                   | 3       |  |  |

|      | 2.1        | CPU Interface                                     | 3       |  |  |

|      |            | 2.1.1 Addressing                                  | 3       |  |  |

|      |            | 2.1.2 Input/Output                                | 3       |  |  |

|      | 2.2        | 8271 Floppy Disc Controller                       | 3       |  |  |

|      | 2.3        | Clock Signals                                     | 4       |  |  |

|      |            | 2.3.1 4MHz Operation                              | 4       |  |  |

|      |            | 2.3.2 Local Oscillator Operation                  | 4       |  |  |

|      |            | 2.3.3 Local Oscillator Setting-Up Procedure       | 4       |  |  |

|      | 2.4        |                                                   |         |  |  |

|      | 2.5        | Ready Signals Generator                           | 6       |  |  |

|      | 2.6        | Floppy Disc Controller/Drive Interface            | 6       |  |  |

|      |            | 2.6.1 Outputs from Floppy Disc Controller         | 6       |  |  |

| _    |            | 2.6.2 Inputs from Floppy Disc Drive Unit          | 8<br>8  |  |  |

| 3.   |            | SOFTWARE PARAMETERS<br>3.1 DOS                    |         |  |  |

|      |            |                                                   | 8       |  |  |

|      | 3.2        | Addressing                                        | 9       |  |  |

|      | 3.3<br>3.4 | Disc Format<br>Disc Errors                        | 9<br>10 |  |  |

|      |            |                                                   |         |  |  |

| 4.   | FLOF       | 11                                                |         |  |  |

|      | 4.1        | Floppy Disc Controller Board to Acorn Bus         | 11      |  |  |

|      | 4.2        | Floppy Disc Controller Board to Floppy Disc Drive | 11      |  |  |

|      |            | (Daisy Chained to Ail Drives)                     |         |  |  |

| 5.   | PAR        | TS LIST                                           | 12      |  |  |

|      | 5.1        | Mechanical Parts                                  | 12      |  |  |

|      | 5.2        | Electrical Parts                                  | 12      |  |  |

01982 Acorn Computers Limited, 12 Fulbourn Road, Cherry Hinton, Cambridge. Written and Produced for Acorn Computers Limited by Arch Technical Publications Limited, St, Lukes House, 5, Walsworth Road, Hitchin, Herts.

400,004

(i)

| TΑ | B | LE | S |

|----|---|----|---|

| TΑ |   | LE | S |

| Table | No.                  | Page |

|-------|----------------------|------|

| 1.    | Addressing           | 9    |

| 2.    | Disc Drive Selection | 9    |

| 3.    | Error Messages       | 10   |

# FIGURES

| Figure | e No.                                  | Page |

|--------|----------------------------------------|------|

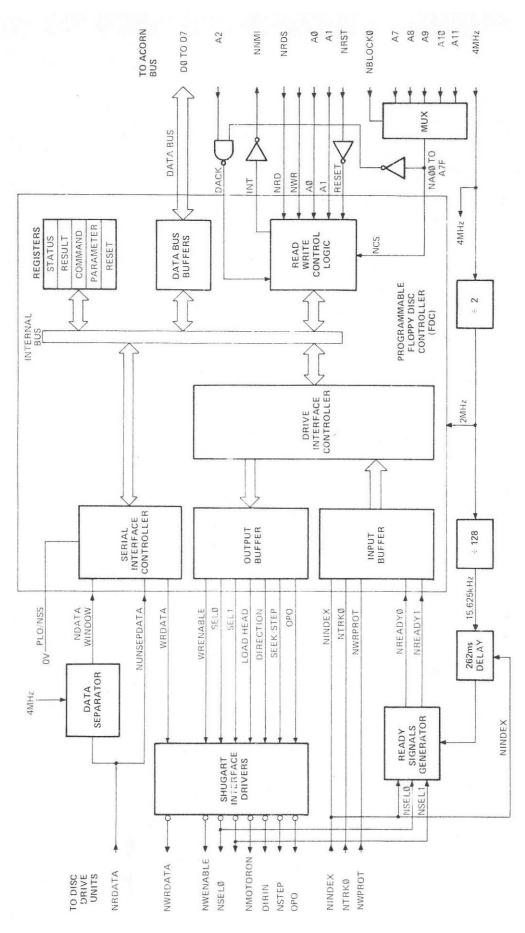

| 1.     | Floppy Disc Controller Block Diagram   | 2    |

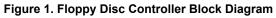

| 2.     | Floppy Disc Controller Write and Read  | 4    |

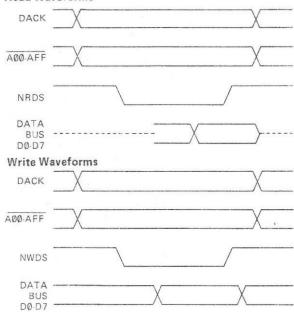

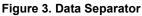

| 3.     | Data Separator                         | 5    |

| 4.     | Ready Signals Generator                | 6    |

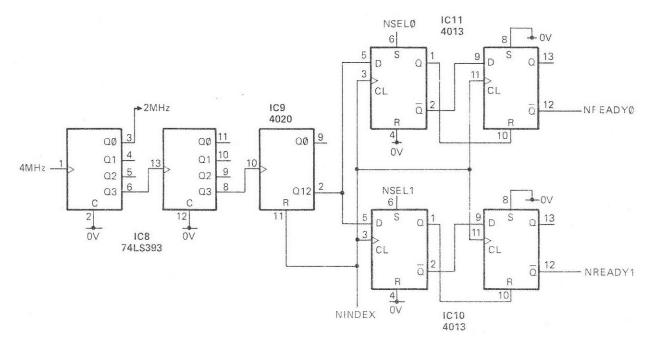

| 5.     | Drive Timing                           | 7    |

| 6.     | Data Timing                            | 8    |

| 7.     | Data Format                            | 10   |

| 8.     | Floppy Disc Controller Circuit Diagram | 13   |

|        |                                        |      |

(ii)

### 1. INTRODUCTION

#### 1.1 GENERAL

The Floppy Disc Controller Board provides an interface to one or two, single or double-sided floppy disc drive units. The board connects to the Acorn Bus and, via a ribbon cable, to the floppy disc drive; multiple floppy disc drives are daisy chained.

Throughout this document, the terms disc and disc drive refer respectively to the flexible plastic dise recording media ("floppy disc", "mini floppy", "flippy", etc) and to the unit containing the drive mechanism and read/write/control electronics into which the disc is inserted.

The board uses the 8271 programmable floppy disc controller device (FDC). The FDC is a high level controller that relieves the CPU of many tasks associated with floppy disc control. It supports a soft sectored format that is IBM 3740 compatible.

The Acorn Disc Operating System (DOS) provides comprehensive commands for the control of disc drives. This is available as ROM pre-programmed to suit a number of floppy disc drive types.

#### 1.2 PRINCIPLES OF OPERATION

A block diagram of the Floppy Disc Controller Board is given on Figure 1.

The FDC executes each data record transfer, writing to or reading from the disc, in three phases. It accepts commands from the CPU, executes the command ( transfers the data record byte by byte), and provides a result (e.g. transfer completed) at the end of the execution phase.

The FDC is controlled by the CPU using various command instructions. Each command is executed autonomously by the FDC. At the end of the execution phase, the FDC flags the CPU (NNMI) which reads the current states (result and status register) before issuing the next command.

Each command defines the mode of operation required, such as Initialization, Read Data, Write Data, etc. and may be supplemented by up to five parameter bytes which further define the command.

At power up or system reset (NRST), the FDC is reset. This halts any commands in progress, clears the registers, and forces the FDC into an idle state. The FDC can also be reset by software using a Reset Command. The FDC is initialized using commands and parameters which specify the various disc drive characteristics such as step rate between tracks, head settling time (pause between final step signal to drive and the writing/reading of data), and head load time.

The head is loaded when a disc is selected, and remains in contact with the disc while stepping over the surface. The head load time is the time between head load and the writing/reading of data.

The final phase of initialization consists of setting the head(s) on each drive equipped to track 0 using a Seek Command. This command causes the FDC to locate the head of the first drive to track 0 and to interrupt the CPU which reads and resets the Result Register. The FDC then tests the second disc drive position. If a drive is present, its head is located to track 0 and the CPU interrupted to read and reset the Result Register for the second drive.

The locating of the head(s) to track 0 ensures that the head position is known, particularly after power up.

Each data transfer (write to or read from disc) consists of three phases. Each phase is initiated by the CPU with all further actions controlled by the FDC. These phases are:

#### COMMAND PHASE

The CPU addresses the FDC to enable its input and output buffers and the command and parameter registers as appropriate and transfers a command ( Table 1) and from zero to five parameter instructions via the Data Bus, to the selected register. The FDC is addressed for each command or parameter transfer.

The command defines the type of transfer required and the parameters define the data, e.g. location ( disc, surface, track, sector) and length of data record.

On completion of the Command Phase, the FDC enters the appropriate Execute Phase.

#### WRITE EXECUTE PHASE

During this phase, each byte of the data record to be written is loaded onto the Data Bus by the CPU and the NWDS signal set active to initiate the writing of that byte.

The CPU addresses the FDC to enable the data input buffers and sets the NWDS signal active to initiate a write transfer. The data byte on the Data Bus is loaded into the FDC, converted to a serial format, clock pulses added and, under control of the FDC transferred to the disc drive at the correct time tc ensure loading to the correct sector. When the data

2

400,004

byte has been transferred, the FDC flags the CPU ( NNMI) to indicate that it is ready to receive the next data byte. The CPU reads the Status Register and the process is repeated for the remaining bytes of the data record. These transfers are synchronized by the FDC setting the NNMI interrupt flag active once every  $64\mu s$ .

#### READ EXECUTE PHASE

The FDC searches for the required data record (defined by the command and parameter instructions). When the first byte is detected, it is read off the disc to the FDC which removes the clock pulses, converts it to a parallel form and flags the CPU using NNMI. The CPU reads the Status Register and then sets NRDS active enabling the transfer of the data byte onto the Acorn Bus. This procedure is repeated for each data byte with each data transfer between the disc, the FDC, and Acorn Bus being synchronized by NNMI once every  $64\mu s$ .

#### **RESULT PHASE**

At the end of the Execute Phase, the Result Register Full bit is set in the Status Register, to indicate that the Command and Execute Phases of the data transfer have been completed.

During each data record transfer, the FDC maintains a tally on the number of data bytes transferred and any errors detected during the transfer. On completion of the data transfer, this data becomes valid in the Result Register. Following the next Status Register read operation, the CPU also reads the Result Register which indicates a successful completion of the command or, if not, the type of error or errors detected. These errors are more fully defined in Section 3.

When the Result Register has been read by the CPU, it is reset and the Status Register is updated to idle.

The FDC automatically unloads the disc head(s) if another command is not received from the CPU within ten revolutions of the disc (2s) after completion of a command.

#### 1.3 LEADING PARTICULARS

#### 1.3.1 Mechanical

| Construction | : | Single Eurocard PCB |

|--------------|---|---------------------|

| Size         | : | 100mm x 160mm       |

#### 1.3.2 Power Supplies

+5V at 150mA.

#### 1.3.3 Connections

Pin connections are given in Section 5.

| Connectors : | Double-sided edge connector to<br>Acorn Bus. TTL signal levels are<br>used, OV to +0.4V = logic 0, +2.<br>4V to +5.25V = logic 1. |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

|              | 32-way ribbon cable to disc drive unit. TTL signal levels are                                                                     |  |  |

drive unit. TTL signal levels are used, OV to +0.4V = logic 0, +2. 4V to +5.25V = logic 1. Outgoing signals are fed via drivers, providing up to 48mA at the logic 0 level.

#### 2. CIRCUIT DESCRIPTION

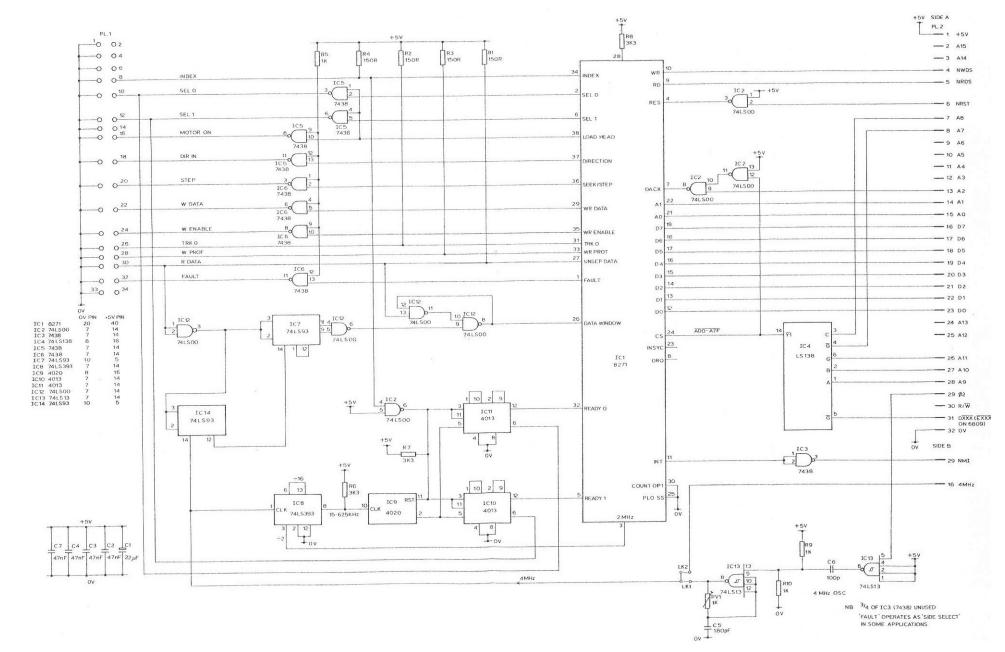

The circuit diagram for the Floppy Disc Controller Board, Figure 8, is filed at the end of this section.

#### 2.1 CPU INTERFACE

#### 2.1.1 Addressing

The Floppy Disc Controller Board is addressed by the CPU on address lines A7 to A11 and the Block  $\emptyset$  signal  $\overrightarrow{OXXX}$ . These signals are decoded by IC4 to provide the chip select signal  $\overrightarrow{A}00-\overrightarrow{A7F}$  to the FD((IC1).  $\overrightarrow{A}00-\overrightarrow{AFF}$  is gated with address bit A2 a IC2/11 and IC2/8 to provide a second chip select signal, DACK, to the FDC.

#### 2.1.2 Input/Output

The transfer of data between the FDC and the CPU is controlled by the read and write signals NRDS and NWDS from the CPU. These signals set the direction of data transfer and synchronize the transfer to or from the data bus lines, D0 to D7 (Figure 2).

#### 2.2 8271 FLOPPY DISC CONTROLLER

The internal structure of the Type 8271 FDC device, ICI is shown in block diagram form on Figure 1.

#### READ/WRITE CONTROL LOGIC

This logic provides address recognition from the CPL via address lines AØ to A2 and A7 to A11, the Block Ø signal  $\overline{OXXX}$  and the Read and Write signals NRDS and NWDS. Commands and any associated parameters on the data bus lines DØ to D7 are passed to the Serial and Drive Interface Controllers and the register via the internal bus.

This logic also generates the Interrupt signal INT ( inverted by IC3 to produce NNW) when the FDC is ready to receive or transmit data over the Data Bus.

#### Read Waveforms

# !

#### REGISTERS

The command and parameter data from the CPU, the status of the current data transfer, and the result of each transfer (successful or error detected) are held in these registers. The Status and Result Registers can be read by the CPU and the Reset Register set by a hardware or software Reset Command.

#### DRIVE INTERFACE CONTROLLER

This logic receives information on the type of transfer between disc and FDC (read or write) and the location of the data to be read or stored. This is transferred to the disc drive via output buffers.

It also receives status information from the disc drives, via input buffers, on the initial position of the disc drive head(s), NTRK0, write protected discs, NWRPROT, and the Index signal NINDEX. It also receives the Drive Ready signals NREADY0 and NREADY1 from the Ready signals generator. This information is used to control the transfer of data via the Serial Interface Controller.

#### SERIAL INTERFACE CONTROLLER

This logic provides the serial/parallel conversion of data between the 8-bit internal bus and the serial read and write lines to the Disc Drive as follows:

- Data to be written to disc is converted from an 8bit parallel form to a serial stream with clock pulses. It is inverted and buffered by IC6/6 before being fed to the Disc Drive. Data read from disc consists of a serial stream with clock pulses. The Data Separator (Section 2. 4) provides timing pulses which enable the Serial Interface Controller to remove the clock pulses and convert the serial data to an 8-bit parallel form.

#### 2.3 CLOCK SIGNALS

The timing for the Floppy Disc Controller Board is provided by the 4MHz clock input from the CPU Board, or may be provided by the local oscillator.

#### 2.3.1 4MHz Operation

The 4MHz clock is divided by IC8 to provide a 2MHz clock signal to the FDC and by IC8 and IC9 to provide a 15.625kHz signal to the Ready Signals Generator Circuit.

### 2.3.2 Local Oscillator Operation

The 4MHz oscillator (IC13 and its associated components, is utilized when operation from the §2 signal is required. IC13/8, RV1, and C5 form a 4MHz, freerunning oscillator. The 4MHz output is synchronized to the rest of the system timing by the §2 signal. This is inverted by IC13/6 and fed via the differentiating circuit of R9, R10 and C6 to trigger IC13/8 at every second cycle of the 4MHz output.

### 2.3.3 Local Oscillator Setting-Up Procedure

The local oscillator, IC13/8 is set up by adjusting RV1 to give an output of 4MHz.

The following equipment is required:

Dual-beam oscilloscope Variable +5V power supply Frequency Generator

Connect the oscilloscope Channel A to IC13 pin 8. Connect the oscilloscope Channel B and the frequency generator to Side A pin 29.

Set the oscilloscope to:

| Amplitude | 2V /cm    |

|-----------|-----------|

| Timebase  | 100ns/cm  |

| Trigger   | Channel B |

Connect the power supply to the board edge connector as follows:

+5V to Side .4 pin 1 0V to Side A pin 32

Set the power supply output to +5.0V.

Set the frequency generator to 1 MHz and at an output level which provides a useable display.

Adjust RV1 to give a stable 4MHz signal on IC13 pin 8 as seen on Channel A, in synchronization with Channel B.

In a 1MHz system the adjustment may be carried out using the system §2 clock signal instead of a signal generator.

# 2.4 DATA SEPARATOR

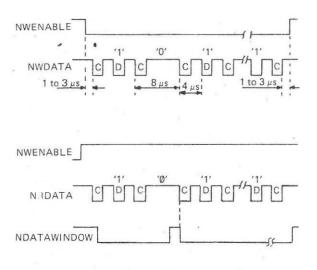

The Data Separator Circuit is illustrated on Figure 3a. It provides identity pulses to the FDC, enabling it to extract the data bits from the combined clock and data pulse stream read off the disc.

The ripple counter, IC14 divides the 4MHz clock by 2 to provide a 2MHz clock signal to a second ripple counter, IC7. The  $\div$ 4 (pin 11) and  $\div$ 16 (pin 9) outputs of IC7 are NANDed by IC12/6 and inverted by IC12/8 to provide a positive going pulse to the FDC NDATAVVINDOW input once every 5µs in the absence of clock and data pulses on the Unseparated Data line (Figure 3b).

400,004

The first dock pulse in a data byte from the disc resets the ripple counters. These counters are reset again by each data logic '1' bit and all the clock pulses, holding the output of the Data Separator Circuit low. Data logic '0' bits do not reset the counters via IC12/3. This allows the counters to run on, producing a positivegoing pulse, to the FDC after 5µs. IC12/11 latches the positive-going NDATAWINDOW signals, until the negative-going edge of the next clock pulse. At the end of a data pulse stream, IC12/11 inhibits the negative-going NDATAWINDOW signal until the next data stream is received.

#### 2.5 READY SIGNALS GENERATOR

This circuit produces a ready signal to IC1 to indicate that the selected drive has a disc fitted and is rotating at approximately the correct speed. (Figure 4).

The 4MHz clock is divided by 256 by the dual counter IC8. The resulting 15.625kHz output is fed to the 14stage ripple counter IC9. Thus, after approximately 262ms from power on the count will have reached 4096 and the Q12 output of IC9 (pin 2) is high.

When a disc drive with a disc installed is switched on (SEL0 or SEL1), the first NINDEX pulse, inverted by IC2/6, resets IC9 to zero. Its Q12 output goes low and the count recommences. If the next NINDEX pulse arrives before the count reaches 4096 (less than 262ms), the low output from IC9 (Q12) is clocked through the dual bistable IC11 to produce NREADY0

for disc drive 1 or through IC10 to produce NREADY1 for disc drive 2.

This process continues while the disc drive is running at the correct speed to produce a continuous Ready signal. As soon as the disc drive is deselected, the appropriate Select signal goes high, setting the corresponding bistable IC10 or IC11, thus disabling the Ready signal.

#### 2.6 FLOPPY DISC CONTROLLER/DRIVE INTERFACE

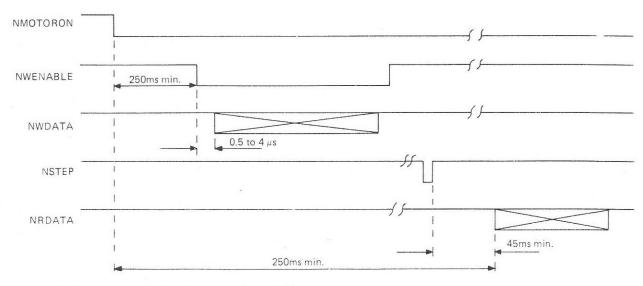

Unless stated otherwise, all signals are active low ( 0V). The signals from the FDC to the drive unit(s) are driven via open collector NAND buffer gates IC5 and IC6 to achieve the power requirements of the interface. Absolute timing of signals across this interface depends on the type of drive in use. Typical signal timings are given on Figures 5 and 6.

#### 2.6.1 Outputs from Floppy Disc Controller

DRIVE SELECT — NSEL0 AND NSEL1 These two lines are multiplexed to provide control of up to four disc drive units. In this application NSEL0 and NSEL1 are used to select the one or two drives equipped.

#### NMOTORON

This signal, inconjunction with NSEL0 and NSEL1 switches on the d.c. drive motors in the disc drive units. Writing to and reading from the discs are delayed by 250ms after NMOTORON becomes

Figure 4. Ready Signals Generator

N.B. All timings quoted are typical and may vary between drive types.

(b) Write and Read

Figure 5. Drive Timing

400,004

Note: C = Clock Pulse; D = Data Pulse

#### Figure 6. Data Timing

active. During idle periods, 2s or more without a data transfer, the NMOTORON signal is disabled to increase motor life.

### HEAD MOVEMENT DIRECTION - DIRIN

This Signal determines the direction of head movement when seeking a track. DIRIN low, in conjunction with NSTEP, causes the head to move towards the centre of the disc. DIRIN high and NSTEP cause the head to move out towards the edge of the disc.

#### NSTEP

Each negative-going, double NSTEP pulse causes the head to move one track position across the disc in the direction determined by the DIRIN signal.

#### READ/WRITE - NWENABLE

NWENABLE low enables the disc write circuits and, when high, enables the disc read circuits.

#### WRITE DATA — NWDATA

This line carries the serial write data to the disc drive units. Write data is enabled onto the selected disc drive unit by the NSEL0 and NSEL1 lines.

#### FAULT or OPO

This output is programmable by DOS to either reset a fault condition signalled by the disc drive or to select a disc surface on a double sided disc. In this application, it is used to select a disc surface. When FAULT is high, the left-hand surface (as viewed from the front of System 5) is selected: when low, FAULT selects the right-hand surface.

#### 2.6.2 Inputs from Floppy Disc Drive Unit

#### TRACK 00 — NTRK0

This signal is low when the head is precisely positioned on track 00.

#### NINDEX

This line is pulsed low each time the disc index mark passes the index detector, once every 200ms. It should be noted that NINDEX is continuously active ( low) while a disc is not fitted in the disc drive unit

#### READ DATA - NRDATA

This line carries the raw serial read data, that is unseparated clock and data signals. Signal NRDATA goes low for each 1 bit (clock and data) read off the disc.

#### WRITE PROTECT - NWPROT

The disc drive unit senses the insertion of a write protected disc and sets signal NWPROT low to prevent overwriting.

#### 3. SOFTWARE PARAMETERS

The storage and retrieval of data on floppy disc is controlled entirely by the System 5 DOS supplied with the system. This control, the formatting of data, and the location of data on a particular disc is unalterable in use. Therefore only a brief description is given.

It should also be noted that the DOS resident in ROM supplied is specific to a particular manufacturer's disc drive unit and, that, where two disc drives are used, they must be of the same type and produced by the same manufacturer.

# 3.1. DOS

The operation of DOS (Disc Operating System) is fully described in the Disc Operating System document.

As soon as a disc drive with a disc loaded is selected, the disc catalogue held in Sectors 0 and 1 of Track 1 is loaded into the CPU's random access memory This catalogue information is assumed to be valid while the disc is rotating. If the disc drive is stopped and restarted for any reason (e.g. disc not required or for a change of disc) the catalogue for the disc in use is reloaded to RAM.

The catalogue contains the disc identity, and the names, size (number of bytes) and location (track and sector) of the files currently held on the disc; doublesided discs contain separate catalogues on each sur-

face. This enables the CPU to control efficiently the transfer of data (files) to and from disc without having to search the whole disc for a file or the next vacant file position.

# 3.2 ADDRESSING

The Floppy Disc Controller Board is addressed by the CPU at AØØ to A7F (hex) via address lines A7 to A11 and signal  $\overrightarrow{OXXX}$ . The various registers within the FDC device are accessed (command from CPU) using address lines AØ to A2 and the NRDS and NWDS signals as shown in Table 1. DACK corresponds to the chip select signal  $\overrightarrow{A00}$ -A7F and A2, and NCS is the chip select signal  $\overrightarrow{A00}$ -A7F generated from A7 to A11 and  $\overrightarrow{OXXX}$ .

| NDACK | NCS | A1 | AØ | NRDS | NWDS | OPERATION        |

|-------|-----|----|----|------|------|------------------|

| 1     | Ø   | Ø  | Ø  | Ø    | 1    | Read Status      |

| 1     | Ø   | Ø  | Ø  | 1    | Ø    | Write Command    |

| 1     | Ø   | Ø  | 1  | Ø    | 1    | Read Result      |

| 1     | Ø   | Ø  | 1  | 1    | Ø    | Write Parameter  |

| 1     | Ø   | 1  | Ø  | 1    | Ø    | Write Reset Reg. |

| Ø     | 1   | Х  | X  | 1    | Ø    | Write Data       |

| Ø     | 1   | Х  | Х  | Ø    | 1    | Read Data        |

| ¢     | Ø   | X  | Х  | Х    | X    | Not Allowed      |

Table 1. FDC Addressing

Up to five command parameters are transferred over the data bus lines D0 to D7. These parameters further define the type of command and identify the required drive disc surface, track and sector, This information is decoded by the FDC to provide the drive and surface select signals SEL and OPO to the disc drives. Further decoding provides the head positioning control signals DIRIN (head direction) and STEP (head stepping) as required.

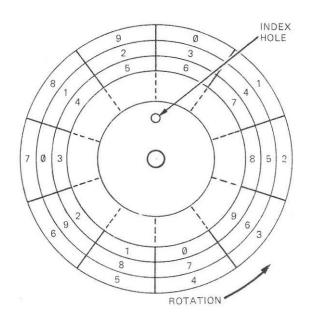

### 3.3 DISC FORMAT

The storage of data on floppy disc is organised by disc and surface, track and sector (Figure 7) as follows:

- Disc (and disc drive). Single or double-sided; one or both surfaces of a disc are used for recording data depending on the type of disc drive fitted.

- Surface. Each surface is formatted in 40 or 80 concentric tracks using the Utilities Disc FORM40 or FORM80 formatting program supplied depending on the type of disc drive in use.

- *Track.* Each track is organised in ten sectors. Track 0 is reserved for the Catalogue File and tracks 1 to 39 or 1 to 79 are used for data storage.

- Sectors. Each sector consists of identity and data fields. A data field holds up to 256 bytes of data. The sectors are recorded on a +3 stagger to obtain file transfers in the minimum number of disc revolutions (Figure 7).

Thus each surface can hold up to 100K bytes of data in 40 track format or 200K bytes of data in 80 track format.

Data is organized in files (data records) with up to 31 files to a disc surface. The number of files is limited by the size of the Catalogue to 31.

A file may be of any length up to the maximum capacity of the disc surface, A file always commences a the beginning of a sector and any unused space at the end of the last sector of a file is filled with random information.

The disc index hole together with a photo-electric detector in the disc drive provides the INDEX signal to the FDC once per disc revolution and also locates the beginning of the first sector on each track.

#### Figure 7. Data Format

# 3.4 DISC ERRORS

The FDC is capable of detecting many error conditions which could arise during the transfer of data to and from disc. These errors are interpreted by software which produces a disc error to the user, either on the VDU or printer, as shown in Table 2.

|           |   | USER ERRORS                                                                                         | SYSTEM ERRORS                                                                                                                                   |       |

|-----------|---|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Crunch    | : | An attempt has been made to for-<br>mat a Write Protected disc.                                     | Disc error Ø8 : During a disc Read operatio<br>clock bit was missing.                                                                           | n a   |

| Disc Full | : | A block large enough to hold the<br>file cannot be found. Periodic<br>housekeeping with the COMPACT | Disc error ØA : During a disc transfer the proce<br>did not respond fast enough (p<br>ably due to a faulty Floppy<br>Interface Board).          | rob-  |

| Disc Prot |   | utility will minimise the occurrence<br>of this error.<br>A Write operation has been attemp-        | Disc error ØC : The CRC (cyclic redundancy ch<br>derived from the ID data read b<br>differed from that which was o<br>nally loaded to the disc. | ack,  |

| Drive ?   |   | ted to a Write Protected disc.                                                                      | Disc error ØE : The CRC derived from the data<br>back on a disc read differed f<br>that baded to the disc.                                      |       |

| File ?    |   | specified.                                                                                          | Disc error 10 : During a transfer the disc stop<br>rotating (probably due to a b<br>inserted disc).                                             |       |

| rut :     | : | File name cannot be found.                                                                          | Disc error 14 : The Floppy Disc Controller                                                                                                      | nter- |

| File Prot | : | A Write operation has been attemp-<br>ted to a Write Protected file.                                | face Board failed to find Trac<br>This error usually results f<br>attempting to access an unforma<br>disc.                                      | rom   |

| Full      | ; | 31 files already exist on the current disc.                                                         | Disc error 18 : The Floppy Disc Controller I<br>face Board failed to find the requ<br>sector. This error usually re                             | ired  |

| Syntax ?  | : | Command is recognized but Syntax error exists.                                                      | from either using an unforma<br>disc, or the disc being corrupte<br>magnetic fields etc.                                                        | tted  |

Table 2. Error Messages

# 4. FLOPPY DISC CONTROLLER CONNECTIONS

# 4.1 FLOPPY DISC CONTROLLER BOARD TO ACORN BUS

| Pin    | Mnemonic | Meaning               | 1/0 |

|--------|----------|-----------------------|-----|

| Side A |          |                       |     |

| 1      | +5V      | +5V Line              | 1   |

| 2      | A15      | Address 15 Not        | 1   |

| 3      | A14      | Lines 14 Used         | 1   |

| 4      | NWDS     | Write Select          | 1   |

| 5      | NRDS     | Read Select           | 1   |

| 6      | NRST     | Reset                 | 1   |

| 7      | A8       |                       |     |

| 8      | A7       |                       |     |

| 9      | A6       | 6                     |     |

| 10     | A5       | 5 Not                 |     |

| 11     | A4       | Address 4 Used        | 1   |

| 12     | A3       | Lines 3               |     |

| 13     | A2       |                       |     |

| 14     | A1       |                       |     |

| 15     | AØ       |                       |     |

| 16     | D7       |                       |     |

| 17     | D6       |                       |     |

| 18     | D5       |                       |     |

| 19     | D4       |                       |     |

| 20     | D3       | Data Lines            | 1/C |

| 21     | D2       |                       |     |

| 22     | D1       |                       |     |

| 23     | DØ       |                       |     |

| 24     | A13      | 13 Not                |     |

| 25     | A12      | 12 Used               |     |

| 26     | A11      | Address               | 1   |

| 27     | A10      | Lines                 |     |

| 28     | A9       |                       |     |

| 29     | Φ2       | System $\Phi$ 2 Clock | 1   |

| 30     | R/NW     | Read/Write Enable -   | 1   |

| 30     |          | Not Used              |     |

| 31     | NBLOCKØ  | Board Enable from CPU | 1   |

| 32     | 0V       | Earth                 |     |

| Side I | 3        |                       |     |

| 16     | 4MHz     | 4MHz Clock            | 1   |

| 29     | NNMI     | Interrupt from FDC    | 0   |

# 4.2 FLOPPY DISC CONTROLLER BOARD TO FLOPPY DISC DRIVE (DAISY CHAINED TO ALL DRIVES)

| Pin | Mnemonic | Meaning                                                                | 1/0 |

|-----|----------|------------------------------------------------------------------------|-----|

| 2   | -        |                                                                        | -   |

| 4   | -        | · — · · · · · ·                                                        | -   |

| 6   | -        | -                                                                      | -   |

| 8   | NINDEX   | Index Signal from Drive                                                | 1   |

| 10  | NSELØ    | Multiplexed Drive                                                      |     |

| 12  | NSEL1    | Select Signals (1 of 4)                                                | 0   |

| 14  | -        | -                                                                      |     |

| 16  | NMOTORON | Motor Drive Enable                                                     | 0   |

| 18  | DIRIN    | Head Movement<br>Direction                                             | 0   |

| 20  | NSTEP    | Moves Head 1 Track in<br>Direction Set by DIRIN                        | 0   |

| 22  | NWDATA   | Data to Disc                                                           | 0   |

| 24  | NWENABLE | Enable Disc Write<br>Circuits                                          | 0   |

|     |          | Enables Disc Read Cir-<br>cuits when High                              |     |

| 26  | NTRKØ    | Indicates Head is pre-<br>cisely positioned on<br>Track ØØ             | 1   |

| 28  | NWPROT   | Disc is Write protected                                                | 1   |

| 30  | NRDATA   | Data from Disc                                                         | 1   |

| 32  | OPO      | Selects Disc Surface for<br>Double Sided Drives.<br>User Programmable. | 0   |

| 34  | -        | -                                                                      | -   |

Odd numbered Pins connected to Earth.

# 5. PARTS LIST

# 5.1 MECHANICAL PARTS

| ITEM | DESCRIPTION<br>Printed Circuit Board<br>Connector, 34-way<br>Connector, 64-way<br>40-pin IC Socket | d, 200.004 | VALUE | QTY<br>1<br>1<br>1<br>1 | PART NO. |

|------|----------------------------------------------------------------------------------------------------|------------|-------|-------------------------|----------|

|      | 16-pin IC Socket                                                                                   | 2          |       |                         |          |

|      | 14-pin IC Socket                                                                                   | 10         |       |                         |          |

# 5.2 ELECTRICAL PARTS

| ITEM                                                                                          | DESCRIPTION                                                                                                                                                                                                                                                          | VALUE                                                                                                        | QTY                                                 | PART NO. |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------|

| C1                                                                                            | Capacitor                                                                                                                                                                                                                                                            | 15µF                                                                                                         | 1                                                   |          |

| C2C4                                                                                          | Capacitor                                                                                                                                                                                                                                                            | 47nF                                                                                                         | 3                                                   |          |

| C5                                                                                            | *Capacitor                                                                                                                                                                                                                                                           | 180pF                                                                                                        | 1                                                   |          |

| C6                                                                                            | *Capacitor                                                                                                                                                                                                                                                           | 100pF                                                                                                        | 1                                                   |          |

| C7                                                                                            | Capacitor                                                                                                                                                                                                                                                            | 47nF                                                                                                         | 1                                                   |          |

| IC1<br>IC2<br>IC3<br>IC4<br>IC5,IC6<br>IC7<br>IC8<br>IC9<br>IC10,IC11<br>IC12<br>IC13<br>IC14 | Integrated circuit<br>Integrated circuit | 8271<br>74LS00<br>7438<br>74LS138<br>7438<br>74LS93<br>74LS393<br>4020<br>4013<br>74LS00<br>74LS13<br>74LS93 | 1<br>1<br>1<br>2<br>1<br>1<br>1<br>2<br>1<br>1<br>1 |          |

| R1.:.R4                                                                                       | Resistor                                                                                                                                                                                                                                                             | 150                                                                                                          | 4                                                   |          |

| R5                                                                                            | Resistor                                                                                                                                                                                                                                                             | 1K                                                                                                           | 1                                                   |          |

| R6R8                                                                                          | Resistor                                                                                                                                                                                                                                                             | 3K3                                                                                                          | 3                                                   |          |

| R9, R10                                                                                       | *Resistor                                                                                                                                                                                                                                                            | 1K                                                                                                           | 2                                                   |          |

| RV1                                                                                           | * Resistor, variable                                                                                                                                                                                                                                                 | 1K                                                                                                           | 1                                                   |          |

\*These components are not used in the Acorn System 5 application.

Figure 8 Floppy Disc Controller Circuit Diagram